Design Follow of Analog ICs (Japanese)

Fabricated ICs

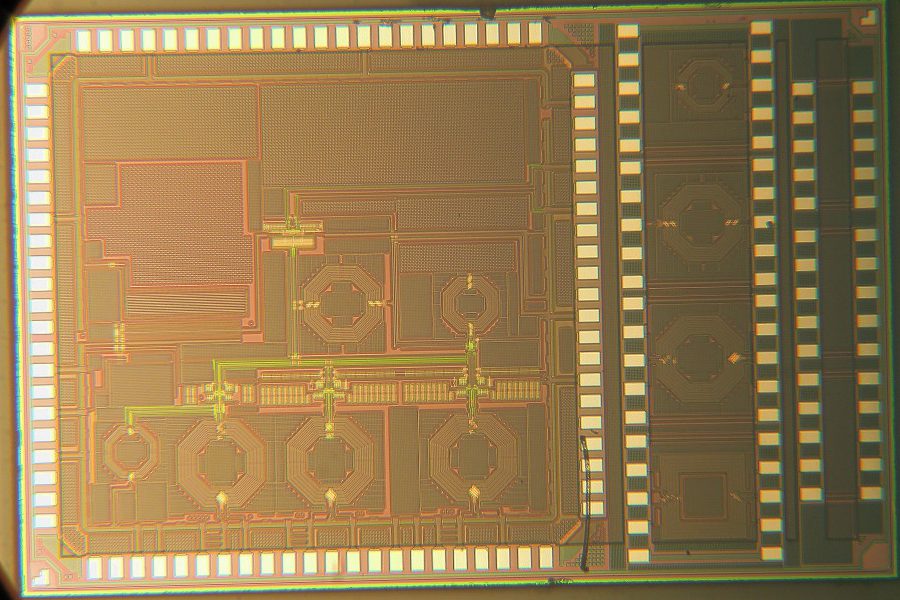

VCO-based ADC and Differential LNA (Feb 2017, T.O.)

- Process: 65 nm SOTB CMOS

- Size: 3.0 x 2.0 mm^2

- Circuits: Voltage-controlled oscillator (VCO), VCO-based A/D converter, Differential low-noise amplifier (LNA), Transformer、Differential inductor

Low-voltage (0.55 V) VCO and Differential LNA (July 2016, T.O.)

- Process: 65 nm SOTB CMOS

- Size: 3.0 x 2.0 mm^2

- Circuits: VCO, Differential LNA, Transformer, Differential inductor

Low-voltage (0.55 V) Differential LNA (Jul 2015, T.O.)

- Process: 65 nm SOTB CMOS

- Size: 2.0 x 1.5 mm^2

- Circuits: Differential LNA, Transformer, Differential inductor